When you open a webpage, load a game, or render a video, your computer performs thousands of calculations and memory transfers in a fraction of a second.

At the heart of this speed lies the cache hierarchy, an organized system that ensures your processor gets the data it needs without unnecessary delays.

What is Cache Hierarchy?

The cache hierarchy is a multi-level storage system in your computer. The idea is simple: store frequently used data in a way that makes it easy and fast to access.

Think of it like this: imagine you’re cooking, and you keep your most-used ingredients, like salt and pepper, on the counter (cache). Less-used items, like flour, are in a cabinet (main memory), and rarely used items are in the pantry (hard drive). The closer and faster the storage, the higher it is in the hierarchy.

The Actual Cache Hierarchy

The cache hierarchy consists of multiple levels of memory, each with specific characteristics tailored to balance speed, size, and cost. Here's a detailed look at the main components:

Beyond the CPU—RAM and Storage

While technically outside the cache memory hierarchy, RAM (main memory) and storage (SSD or HDD) play supporting roles:

- RAM: Stores active data and programs, slower but larger than all cache levels combined.

- Storage Drives: Store permanent data; significantly slower than RAM but offer massive capacity.

How the Cache Hierarchy Works

The cache hierarchy operates based on a principle called locality of reference:

- Temporal Locality: If data is accessed once, it’s likely to be accessed again soon.

- Spatial Locality: If one memory address is accessed, nearby addresses are likely to be accessed too.

Here’s what happens when the CPU processes data:

- Check L1 Cache: The CPU first looks in the L1 cache. If the data is there (a cache hit), it’s processed immediately.

- Fallback to L2 and L3: If L1 doesn’t have the data (a cache miss), the CPU searches L2, then L3.

- Main Memory: If the data isn’t in any cache, the CPU fetches it from RAM, which is significantly slower.

- Store for Future Use: Once fetched, the data is stored in the cache for faster access next time.

This layered approach ensures that frequently used data stays close to the CPU, minimizing delays and maximizing efficiency.

Write Allocation Strategies

Reads aren't the only thing caches manage—writes introduce their own design trade-offs. When new data is written to memory, the system needs to decide how (and whether) that data gets placed into the cache. This is where write allocation strategies come in:

Each method balances latency, memory bandwidth, and data consistency. Most modern CPUs use a hybrid approach depending on the workload and cache level.

Cache Replacement Policies Explained

When a cache is full, and new data needs to be stored, the system has to make a decision: what do we throw out to make room? That’s where cache replacement policies come in. These algorithms govern which data gets evicted when space runs out.

Here are the most common strategies:

Each policy is a trade-off between performance, complexity, and how well it fits a specific workload. CPUs tend to favor LRU or variants because they balance recentness with simplicity.

In contrast, GPU caches or simpler edge caches may use FIFO or Random for speed and predictability.

Inclusive vs. Exclusive Cache Hierarchy

Beyond replacement policies, another critical design factor is whether caches share data across levels or split it between them.

This affects both performance and how much useful data can be stored at once.

Intel often uses inclusive caches, while AMD leans toward exclusive hierarchies. Each path has its own trade-offs, especially in multi-core performance tuning.

Common Cache Hierarchy Challenges

Even with its benefits, the cache hierarchy isn’t without its issues. Here are some common challenges:

1. Cache Misses

- Cold Miss: The data has never been loaded into the cache before.

- Capacity Miss: The cache isn’t large enough to hold all required data.

- Conflict Miss: Two pieces of data map to the same cache location, causing overwrites.

2. Coherence Problems

In multi-core systems, if one core updates data in its cache, other cores may have outdated versions. This is solved using cache coherence protocols like MESI (Modified, Exclusive, Shared, Invalid).

3. Latency Bottlenecks

As cache levels increase in size, latency grows. While L1 is extremely fast, L3 can introduce slight delays compared to higher levels.

{{cool_component}}

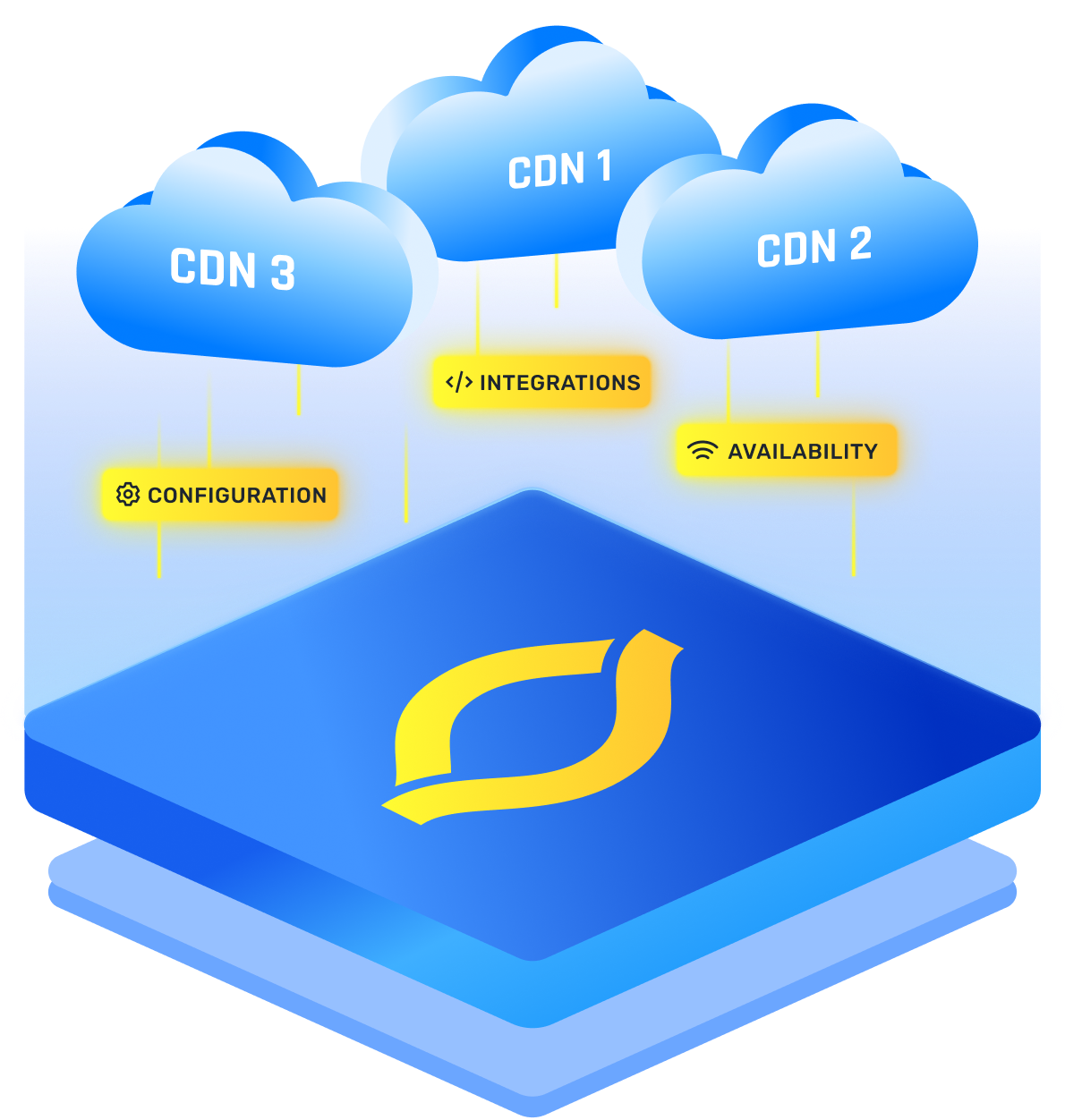

Online Content Caching Hierarchy

Now, let’s talk about how cache-control works for online content.

When you visit a website, watch a YouTube video, or download a file, caching ensures that the data you access is stored closer to you for faster retrieval.

This kind of caching doesn’t involve CPU layers but instead relies on content delivery networks (CDNs) and local storage. Here’s how it works:

- Browser Cache: Your web browser stores elements like images, scripts, and stylesheets locally on your device. This means the next time you visit the same website, it loads faster because it doesn’t have to re-download everything.

- Content Delivery Networks (CDNs): These are distributed servers placed worldwide to store copies of website content. When you request a webpage, the CDN serves it from the closest server to minimize latency.

- Edge Caching: Similar to L1 in CPU caching, edge servers are geographically closer to users and provide rapid delivery of frequently requested content.

- Application Caching: Apps like YouTube or Spotify store chunks of data locally on your device for seamless playback, even if your internet connection is unstable.

CPU Cache vs. Online Content Caching Hierarchies

Although CPU and online caching operate in different domains, they share some underlying principles:

Both systems optimize the process of fetching frequently accessed data and minimize delays caused by repeated requests to the original source.

Unified Memory vs Traditional Cache Hierarchy

In traditional computing architectures, memory is tiered—CPU registers, multiple cache levels (L1–L3), RAM, then storage—each with trade-offs in latency, bandwidth, and capacity.

This is the core principle behind a cache hierarchy: faster, smaller memory layers sit closer to the processor, while slower, larger layers are further away.

Unified memory, by contrast, flattens this model.

Rather than fragmenting memory between CPU, GPU, and other accelerators, unified memory systems pool everything into a single addressable space. This allows data to move freely between compute units without manual copying or managing separate memory pools.

Unified memory simplifies programming and improves performance for tasks that require frequent CPU–GPU data exchange—such as machine learning or real-time graphics rendering.

However, traditional cache hierarchies still dominate general-purpose CPUs because they offer fine-grained control and ultra-low latency for instruction-level execution.

Conclusions

The concept of cache hierarchy spans both hardware and online content delivery. In CPUs, it’s all about layers of memory working together to ensure your processor doesn’t slow down. Online, it’s about strategically placing data closer to users to deliver a fast and seamless experience.

FAQs

1. Can larger caches improve computing speed?

Yes, larger caches reduce the number of trips to slower memory by storing more data close to the processor. This improves computing speed by minimizing access latency across cache levels, especially when working with large datasets or complex workloads. However, larger caches also tend to have slightly higher latency than smaller ones.

2. How do misses affect cache performance?

Cache misses force the CPU to fetch data from slower memory tiers (L2, L3, or RAM), introducing delays. The deeper the miss in the cache hierarchy, the greater the performance penalty. Frequent misses can bottleneck execution, which is why optimizing hit rates across all cache levels is critical.

3. What is spatial locality in cache systems?

Spatial locality refers to the tendency of programs to access data located near recently accessed memory addresses. Caches use this pattern to load entire blocks of data—not just a single byte—anticipating nearby access. It's a key reason why well-structured loops and data access patterns yield better cache efficiency.